user documentation

# IPC/REL12-1AE

$Document\ Ordercode:\ DOC/IPC\_REL12-E$

| Revision | Date       | Author    | Modification         |

|----------|------------|-----------|----------------------|

| 1.0      | 23.11.2005 | U. Müller |                      |

| 1.1      | 15.05.2007 | U. Müller | minor corrections    |

| 1.2      | 18.08.2009 | U. Müller | references corrected |

|          |            |           |                      |

|          |            |           |                      |

|          |            |           |                      |

|          |            |           |                      |

| -        |            |           |                      |

|          |            |           |                      |

| -        |            |           |                      |

| -        |            |           |                      |

# Contents

| 1 | Intro | duction   |                                         | 4  |

|---|-------|-----------|-----------------------------------------|----|

|   | 1.1.  | Genera    | ıl Remarks                              | 4  |

|   | 1.2.  | Conten    | ats of this Documentation               | 4  |

|   | 1.3.  | Additio   | onal Products and Documents             | 4  |

|   |       | 1.3.1.    | Hardware Products                       | 4  |

|   |       | 1.3.2.    | Software Products                       | 5  |

|   |       | 1.3.3.    | Documents                               | 5  |

|   | 1.4.  | Items d   | delivered                               | 5  |

|   | 1.5.  | Installa  | ation                                   | 5  |

|   | 1.6.  | Safety    | Recommendations and Warnings            | 5  |

|   | 1.7.  | Life Cy   | ycle Information                        | 6  |

|   |       | 1.7.1.    | Transportation and Storage              | 6  |

|   |       | 1.7.2.    | Assembly and Installation               | 6  |

|   |       | 1.7.3.    | Operation                               | 6  |

|   |       | 1.7.4.    | Maintenance and Repair                  | 6  |

|   |       | 1.7.5.    | Disposal                                | 6  |

| 2 | Prod  | uct Desc  | ription                                 | 7  |

|   | 2.1.  | Feature   | es                                      | 7  |

|   | 2.2.  | Connec    | ctor Assignments                        | 9  |

|   | 2.3.  | Bus Int   | terface (PC/104)                        | 11 |

| 3 | Hard  | ware De   | scription                               | 12 |

|   | 3.1.  | Overvi    | ew                                      | 12 |

|   | 3.2.  | Relay (   | Outputs                                 | 13 |

|   | 3.3.  | Transis   | stor Outputs                            | 13 |

|   | 3.4.  | Memor     | ry and I/O Resources                    | 13 |

|   |       | 3.4.1.    | General Memory Layout and Configuration | 13 |

|   |       | 3.4.2.    | General I/O Layout and Configuration    | 13 |

|   |       | 3.4.3.    | Board Base Address Configuration        | 14 |

|   |       | 3.4.4.    | Other Configuration Options             | 15 |

| 4 | Prog  | ramming   | g Information                           | 16 |

|   | 4.1.  | Overvi    | ew                                      | 16 |

|   | 4.2.  | Registe   | er Model and Bit-Utilization            | 16 |

|   | 4.3.  | Memor     | ry and I/O Resources                    | 16 |

|   |       | 4.3.1.    | General Memory Layout and Configuration | 16 |

|   |       | 4.3.2.    | General I/O Layout and Configuration    | 16 |

| 5 | Tech  | nical Dat | ta                                      | 19 |

|   | 5.1.  | Genera    | ıl Electrical Data                      | 19 |

|   | 5.2.  | Mechai    | nical Data                              | 21 |

| 6  | 5 Firmware |                                                            |    |  |  |  |

|----|------------|------------------------------------------------------------|----|--|--|--|

| 7  | Prod       | uct Revision History                                       | 23 |  |  |  |

|    | 7.1.       | Hardware                                                   | 23 |  |  |  |

|    | 7.2.       | Firmware                                                   | 23 |  |  |  |

| 8  | Manı       | ufacturer Information                                      | 24 |  |  |  |

|    | 8.1.       | Contact                                                    | 24 |  |  |  |

|    | 8.2.       | Warranty                                                   | 24 |  |  |  |

|    |            | Tables                                                     |    |  |  |  |

|    | ıb. 1      | Process Interface Connector P1                             |    |  |  |  |

| Ta | ıb. 2      | Transistor Output Connector P2                             |    |  |  |  |

|    | ıb. 3      | PC/104 Bus Connectors PA/PB, PC/PD                         |    |  |  |  |

|    | ıb. 4      | I/O Address Space Layout                                   |    |  |  |  |

|    | ıb. 5      | I/O Base Address Configuration Switch S1                   |    |  |  |  |

|    | ıb. 6      | Configuration Options Switch S1                            |    |  |  |  |

|    | ıb. 7      | Factory Programming Header J2 (1x4 pin)                    |    |  |  |  |

| Ta | ıb. 8      | I/O Address Space Layout                                   |    |  |  |  |

| Ta | ıb. 9      | Utilization of the individual Bit (READ-Registers)         |    |  |  |  |

| Ta | ıb. 10     | Utilization of the individual Bit (WRITE-Registers)        | 18 |  |  |  |

| Ta | ıb. 11     | Interface Specifications and Programming for Relay Outputs | 18 |  |  |  |

| Ta | ıb. 12     | General Absolute Maximum Ratings                           | 19 |  |  |  |

| Ta | ıb. 13     | General Recommended Operating Conditions                   | 20 |  |  |  |

| Ta | ıb. 14     | General Electrical Characteristics                         | 20 |  |  |  |

| Ta | ıb. 15     | General Switching Characteristics                          | 20 |  |  |  |

| Та | ıb. 16     | Hardware Revision State                                    | 23 |  |  |  |

|    |            | Figures                                                    |    |  |  |  |

|    | g. 1       | Block Diagram                                              |    |  |  |  |

|    | g. 2       | Process Interface Connector P1                             |    |  |  |  |

|    | g. 3       | Transistor Output Connector P2                             |    |  |  |  |

|    | g. 4       | Board Layout                                               |    |  |  |  |

| Fi | g. 5       | Mechanical Outline                                         | 21 |  |  |  |

# 1 Introduction

#### 1.1. General Remarks

The content and presentation of this document has been carefully checked. No responsibility is accepted for any errors or omissions in the documentation.

Note that the documentation for the products is constantly revised and improved. The right to change this documentation at any time without notice is therefore reserved.

Syslogic is grateful for any help referring to errors or for suggestions for improvements.

The following registered trademarks are used:

IBM-PC, PC/AT, PS/2 trademarks of IBM Corporation

FBCube, EUROLOG, trademarks of Syslogic Datentechnik AG

#### 1.2. Contents of this Documentation

This document addresses to system integrators, programmers and instructed installation and maintenance personal working with the IPC system. It provides all information needed to configure, setup and program the relays interface board IPC/REL12-1AE. For complete information also the documentation of the mounted CPU board and communications and I/O boards must be consulted. As the IPC/REL12 board may be delivered in various versions with optional hardware blocks the standard version (IPC/REL12-1AE) is described here, which includes all hardware function blocks.

#### 1.3. Additional Products and Documents

#### 1.3.1. Hardware Products

The following hardware products are useful together with the IPC/REL12 board:

- IPC startup guide and tools

- IPC/NETIPC CPU boards

- IPC communication boards

- IPC I/O boards

(see product catalog for details)

#### 1.3.2. Software Products

The following software products are useful together with the IPC/REL12 board:

- Firmware for IPC CPU boards: e.g. IPC/NETIPCFW-1A

- Sample program code and utilities for x86 based FBCube systems:

IPC/IOCOMSW-1A

#### 1.3.3. Documents

The following documents are *required* for correct installation and operation of the IPC/REL12 board:

- DOC/CUBINST: User Documentation for FBCube Installation

**Note:** also contains the necessary information related to the "ce"-certification of the products

- User Documentation for Basic Firmware (dependent on CPU board)

- DOC/IPC\_IOCOMSW: User Documentation for Programming Examples and Utilities

#### 1.4. Items delivered

The IPC/REL12 module is delivered without any mechanical mounting material. The user should order the required mechanical mounting material according to his needs (open frame mounting, 19"-rack mounting, DIN-rail mounting etc.). Note that the technical documentation is not part of the delivery and must be ordered separately or downloaded from the Internet.

A CPU board, power supply board and enclosure are necessary to build a complete system. All items must be ordered separately and installed according to the respective user documentations. A standard base configuration could be as follows:

- IPC system with NETIPC-2A CPU board and free slot for I/O board: IPC/COMPACT2-2E

- external power adapter

- CompactFlash

Note: Mounting procedure is described in DOC/COMPACT2-2E

#### 1.5. Installation

The installation of the IPC system is described in the documentation DOC/CUBINST.

The firmware configuration and download is described in the appropriate firmware documentation.

#### **Important Note**

Before applying power to the IPC system the all boards must be correctly configured and mounted (please consult User Documentation of the selected boards).

### 1.6. Safety Recommendations and Warnings

The products are intended for measurement, control and communications applications in industrial environments. The products must be assembled and installed by specially trained people. The strict observation of the assembly and installation guidelines is mandatory.

The use of the products in systems in which the life or health of persons is directly dependent (e.g. life support systems, patient monitoring systems, etc.) is not allowed.

The use of the products in potentially explosive atmospheres requires additional external protection circuitry which is not provided with the products.

In case of uncertainty or of believed errors in the documentation please immediately contact the manufacturer (address see chapter 8). Do not use or install the products if you are in doubt. In any case of misuse of the products, the user is solely liable for the consequences.

## 1.7. Life Cycle Information

#### 1.7.1. Transportation and Storage

During transportation and storage the products must be in their original packing. The original packing contains an antistatic bag and shock-absorbing material. It is recommended, to keep the original packing in case of return of the product to the factory for repair. Note that the packing is recyclable.

#### 1.7.2. Assembly and Installation

Observe the EMI-precautions against static discharge. Carefully read the assembly and installation documentation (Document DOC/CUBINST) before unpacking the products. Make sure that you have all the necessary items ready (including all the small parts). Follow the assembly guidelines in DOC/CUBINST strictly.

The installation procedures (contained in document DOC/CUBINST) must be strictly observed. Note that deviations from the installation guidelines may result in degraded operational reliability or in unfavourable EM-radiation or EM-susceptibility.

#### 1.7.3. Operation

The operating environment must guarantee the environmental parameters (temperature, power supply, etc.) specified in the technical specification section of the product manuals.

The main functionality of the system is defined by the application programs running on the system. The application programs are not part of the delivery by Syslogic but are defined, developped and tested by the customer or a system-integrator for each specific application. Refer to the respective documentation for more information.

#### 1.7.4. Maintenance and Repair

The product features error- and malfunction-detection circuitry. Diagnostic information gathered is transferred to the applications software where it can be used. In the rare case of a module hardware-failure or malfunction, the complete module should be exchanged. The faulty module must be returned to the factory for repair. Please use whenever possible the original packing for return of the product (EMI and mechanical protection).

#### 1.7.5. Disposal

At the end of the lifespan the product must be properly disposed. IPC products contain a multitude of elements and must be disposed like computer parts. Some of the IPC products contain batteries which should be properly disposed.

# **2 Product Description**

#### 2.1. Features

The 12 channel relays interface board IPC/REL12-1AE provides twelve potential-free mechanical contacts. Make and break contact connection is available on the interface connector.

In addition 8 open collector transistor outputs are available for driving light loads like relays or LEDs.

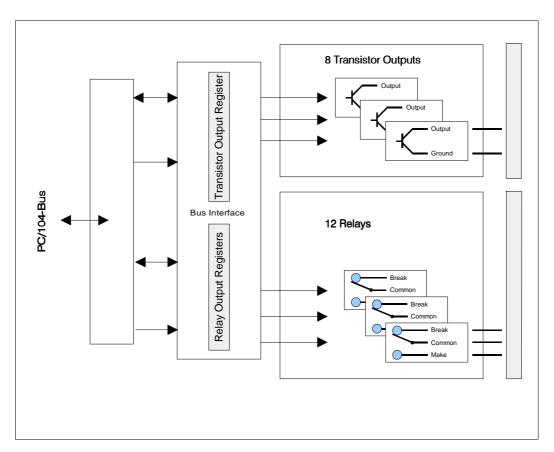

The block diagram of the board is shown in Fig. 1.

Fig. 1 Block Diagram

#### The main functional elements are:

- PC/104 local bus interface

- board base address selection switch

- 12 relays with make and break contacts

- 8 open collector transistor outputs

# 2.2. Connector Assignments

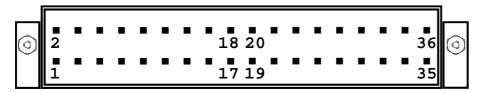

The relay connector/pin assignment for the board is shown in Tab. 1.

Mating plug type: Weidmüller B2L 3.5/36F SN SW (Weidmüller ordering code 1748320000)

Field wiring: AWG18...28 / 0.5-1.0 mm<sup>2</sup>

Fig. 2 Process Interface Connector P1

|     | Process Interface Signal | I/O Connector |                         |

|-----|--------------------------|---------------|-------------------------|

| Pin |                          | Pin           |                         |

| 1   | Relay 0 Make Contact     | 2             | Relay 1 Make Contact    |

| 3   | Relay 0 Common Contact   | 4             | Relay 1 Common Contact  |

| 5   | Relay 0 Break Contact    | 6             | Relay 1 Break Contact   |

| 7   | Relay 2 Make Contact     | 8             | Relay 3 Make Contact    |

| 9   | Relay 2 Common Contact   | 10            | Relay 3 Common Contact  |

| 11  | Relay 2 Break Contact    | 12            | Relay 3 Break Contact   |

| 13  | Relay 4 Make Contact     | 14            | Relay 5 Make Contact    |

| 15  | Relay 4 Common Contact   | 16            | Relay 5 Common Contact  |

| 17  | Relay 4 Break Contact    | 18            | Relay 5 Break Contact   |

| 19  | Relay 6 Make Contact     | 20            | Relay 7 Make Contact    |

| 21  | Relay 6 Common Contact   | 22            | Relay 7 Common Contact  |

| 23  | Relay 6 Break Contact    | 24            | Relay 7 Break Contact   |

| 25  | Relay 8 Make Contact     | 26            | Relay 9 Make Contact    |

| 27  | Relay 8 Common Contact   | 28            | Relay 9 Common Contact  |

| 29  | Relay 8 Break Contact    | 30            | Relay 9 Break Contact   |

| 31  | Relay 10 Make Contact    | 32            | Relay 11 Make Contact   |

| 33  | Relay 10 Common Contact  | 34            | Relay 11 Common Contact |

| 35  | Relay 10 Break Contact   | 36            | Relay 11 Break Contact  |

Tab. 1 Process Interface Connector P1

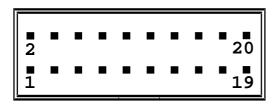

The transistor output connector/pin assignment for the board is shown in Tab. 2.

Fig. 3 Transistor Output Connector P2

| I/O Connector | Process Interface Signal | I/O Connector |                        |

|---------------|--------------------------|---------------|------------------------|

| Pin           |                          | Pin           |                        |

| 1             | Output D0                | 2             | Pullup Resistor to VCC |

| 3             | Output D1                | 4             | Pullup Resistor to VCC |

| 5             | Output D2                | 6             | Pullup Resistor to VCC |

| 7             | Output D3                | 8             | Pullup Resistor to VCC |

| 9             | Output D4                | 10            | Pullup Resistor to VCC |

| 11            | Output D5                | 12            | Pullup Resistor to VCC |

| 13            | Output D6                | 14            | Pullup Resistor to VCC |

| 15            | Output D7                | 16            | Pullup Resistor to VCC |

| 17            | Ground                   | 18            | Vext                   |

| 19            | Ground                   | 20            | Vext                   |

Tab. 2 Transistor Output Connector P2

# 2.3. Bus Interface (PC/104)

The PC/104 bus interface of the IPC/REL12 allows connection to a wide range of processor boards. The bus interface is described in the IEEE 996 and 996.1 standards documentation. The bus connector pinout is shown in Tab. 2. Depending on the board version the bus connector may have a different form factor but the position of the PC/104 signals stay the same. This enables to support additional bus signals (Vbatt, Power, etc) on one single connector block.

| Pin |   | Signal Name   | Pi  | n | Signal Name | Pi       | n      | Signal Name    | Pi       | in     | Signal Name     |

|-----|---|---------------|-----|---|-------------|----------|--------|----------------|----------|--------|-----------------|

|     |   |               |     |   |             | A 1      |        | IOCHCK#        | D1       | 0      | CND             |

| P11 |   |               | P12 |   |             | A1<br>A2 | ⊗<br>⊗ | IOCHCK#<br>SD7 | B1<br>B2 | ⊗<br>⊗ | GND<br>RESETDRV |

|     |   | CND           | 1   |   | CND         | A3       |        | SD6            | B3       |        | +5V             |

| 1   | 8 | GND           |     | 8 | GND         |          | 8      |                | 1        | 8      |                 |

| 2   | 8 | no connection | 2   | 8 | +5V         | A4       | 8      | SD5            | B4       | 8      | IRQ9            |

| 3   | 8 | no connection | 3   | 8 | TRIGGER*    | A5       | 8      | SD4            | B5       | 8      | -5V (not used)  |

| 4   | 8 | Vbatt         | 4   | 8 | STOP*       | A6       | 8      | SD3            | B6       | 8      | DRQ2            |

|     |   |               |     |   |             | A7       | 8      | SD2            | В7       | 8      | -12V (not used) |

|     |   |               |     |   |             | A8       | 8      | SD1            | B8       | 8      | 0WS#            |

| D0  | 8 | GND           | C0  | 8 | GND         | A9       | 8      | SD0            | B9       | 8      | +12V (not used) |

| D1  | 8 | MEMCS16#      | C1  | 8 | SBHE#       | A10      | 8      | IOCHRDY        | B10      | 8      | (KEY)           |

| D2  | 8 | IOCS16#       | C2  | 8 | LA23        | A11      | 8      | AEN            | B11      | 8      | SMEMW#          |

| D3  | 8 | IRQ10         | C3  | 8 | LA22        | A12      | 8      | SA19           | B12      | 8      | SMEMR#          |

| D4  | 8 | IRQ11         | C4  | 8 | LA21        | A13      | 8      | SA18           | B13      | 8      | IOW#            |

| D5  | 8 | IRQ12         | C5  | 8 | LA20        | A14      | 8      | SA17           | B14      | 8      | IOR#            |

| D6  | 8 | IRQ15         | C6  | 8 | LA19        | A15      | 8      | SA16           | B15      | 8      | DACK3#          |

| D7  | 8 | IRQ14         | C7  | 8 | LA18        | A16      | 8      | SA15           | B16      | 8      | DRQ3            |

| D8  | 8 | DACK0#        | C8  | 8 | LA17        | A17      | 8      | SA14           | B17      | 8      | DACK1#          |

| D9  | 8 | DRQ0          | C9  | 8 | MEMR#       | A18      | 8      | SA13           | B18      | 8      | DRQ1            |

| D10 | 8 | DACK5#        | C10 | 8 | MEMW#       | A19      | 8      | SA12           | B19      | 8      | REFRESH#        |

| D11 | 8 | DRQ5          | C11 | 8 | SD8         | A20      | 8      | SA11           | B20      | 8      | SYSCLK          |

| D12 | 8 | DACK6#        | C12 | 8 | SD9         | A21      | 8      | SA10           | B21      | 8      | IRQ7            |

| D13 | 8 | DRQ6          | C13 | 8 | SD10        | A22      | 8      | SA9            | B22      | 8      | IRQ6            |

| D14 | 8 | DACK7#        | C14 | 8 | SD11        | A23      | 8      | SA8            | B23      | 8      | IRQ5            |

| D15 | 8 | DRQ7          | C15 | 8 | SD12        | A24      | 8      | SA7            | B24      | 8      | IRQ4            |

| D16 | 8 | +5V           | C16 | 8 | SD13        | A25      | 8      | SA6            | B25      | 8      | IRQ3            |

| D17 | 8 | MASTER#       | C17 | 8 | SD14        | A26      | 8      | SA5            | B26      | 8      | DACK2#          |

| D18 | 8 | GND           | C18 | 8 | SD15        | A27      | 8      | SA4            | B27      | 8      | TC              |

| D19 | 8 | GND           | C19 | 8 | (KEY)       | A28      | 8      | SA3            | B28      | 8      | BALE            |

|     |   |               |     |   | ,           | A29      | 8      | SA2            | B29      | 8      | +5V             |

|     |   |               |     |   |             | A30      | 8      | SA1            | B30      | 8      | OSC             |

|     |   |               |     |   |             | A31      | 8      | SA0            | B31      | 8      | GND             |

|     |   |               |     |   |             | A32      | 8      | GND            | B32      | 8      | GND             |

Tab. 3 PC/104 Bus Connectors PA/PB, PC/PD

# **3 Hardware Description**

## 3.1. Overview

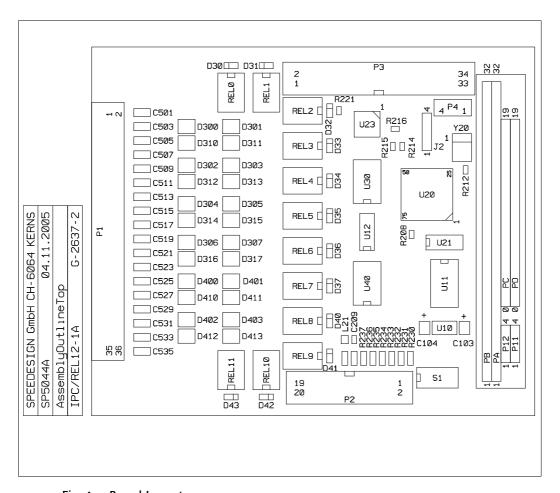

Fig. 4 Board Layout

#### 3.2. Relay Outputs

The twelve Relay outputs provide make and break contacts for connection of external AC or DC loads. Each contact is protected with a transient voltage supressor and high voltage capacitor to earth/shield.

Relay outputs are galvanically isolatet from logic/transistor outputs and from the other relay outputs.

See technical data section for output ratings.

#### 3.3. Transistor Outputs

The eight transistor outputs (open collector) may be used to drive small external loads like relays or LEDs. On the connector a pullup connection to Vcc is provided for each transistor output on the opposite pin for easy direct connection of LEDs. All outputs share a common ground.

If driving external relays or inductive loads a clamping circuit is available on the Vext pins of the connector to protect the transistors. Connect the external supply of the relays or inductive load to Vext pin to activate the clamping circuit, otherwise leave it open/unconnected.

The transistor outputs are not isolated from logic and therefor should only be used for internal loads or externally protected loads.

See technical data section for output ratings.

#### 3.4. Memory and I/O Resources

#### 3.4.1. General Memory Layout and Configuration

The IPC/REL12 board does not use any memory resources.

#### 3.4.2. General I/O Layout and Configuration

| Address      | Device / Register        | Remarks |

|--------------|--------------------------|---------|

| Base + 0003H | Control/Status Registers |         |

| Base + 0407H | Digital I/O Registers    |         |

| Base + 080FH | reserved                 |         |

Tab. 4 I/O Address Space Layout

#### 3.4.3. Board Base Address Configuration

The base address of the IPC/REL12 can be selected in the range 0x200..0x3FF and 0x8200..0x83FF according to Tab. 4. The IPC/REL12 board uses a block of 16 bytes in the I/O space, starting at the configured base address. The base address is defined by setting the sliders of switch S1. Several IPC/REL12 boards (with different base addresses!) can be used in the same system.

**CAUTION**: Each board in the IPC system must have its own, unique address range. Overlapping address ranges may damage the boards.

| Switch S1 / No | 6   | -   | -   | -   | -   | -   | -  | 5   | 4         | 3   | 2         | 1   |     |

|----------------|-----|-----|-----|-----|-----|-----|----|-----|-----------|-----|-----------|-----|-----|

| address line   | A15 | A14 | A13 | A12 | A11 | A10 | A9 | A8  | <b>A7</b> | A6  | <b>A5</b> | A4  | A30 |

| I/O address    |     |     |     |     |     |     |    |     |           |     |           |     |     |

| 0x0200         | on  | 0   | 0   | 0   | 0   | 0   | 1  | on  | on        | on  | on        | on  | 0   |

| 0x0210         | on  | 0   | 0   | 0   | 0   | 0   | 1  | on  | on        | on  | on        | off | 0   |

|                |     | 0   | 0   | 0   | 0   | 0   | 1  |     |           |     |           |     | 0   |

| 0x03E0         | on  | 0   | 0   | 0   | 0   | 0   | 1  | off | off       | off | off       | on  | 0   |

|                |     | 0   | 0   | 0   | 0   | 0   | 1  |     |           |     |           |     | 0   |

| 0x8200         | off | 0   | 0   | 0   | 0   | 0   | 1  | on  | on        | on  | on        | on  | 0   |

| 0x8210         | off | 0   | 0   | 0   | 0   | 0   | 1  | on  | on        | on  | on        | off | 0   |

|                |     | 0   | 0   | 0   | 0   | 0   | 1  |     |           |     |           |     | 0   |

| 0x83F0         | off | 0   | 0   | 0   | 0   | 0   | 1  | off | off       | off | off       | off | 0   |

Tab. 5 I/O Base Address Configuration Switch S1

**Note:** Switch off: 1 Switch on: 0

# 3.4.4. Other Configuration Options

| Switch S1 | Configuration | Remarks       |

|-----------|---------------|---------------|

| 7         | reserved      | do not change |

| 8         | reserved      | must be OFF!  |

Tab. 6 Configuration Options Switch S1

| Pin Number | Signal | Remarks    |

|------------|--------|------------|

| 1          | TCK    | do not use |

| 2          | TDO    | do not use |

| 3          | TMS    | do not use |

| 4          | TDI    | do not use |

Tab. 7 Factory Programming Header J2 (1x4 pin)

# **4 Programming Information**

#### 4.1. Overview

The programming of the IPC/REL12 board is done with standard I/O read and write operations. For detailled information refer to the CPU board's user documentation, firmware documentation and other related documents as listed in paragraph 1.3.

# 4.2. Register Model and Bit-Utilization

Warning: Do not read from or write into addresses not defined in the register model!

All registers of the IPC/REL12 are located in the I/O address space. The register model is shown in Tab. 7 and the utilization of the individual bits is listed in Tab. 8 and Tab. 10. The programming of the relays outputs in Tab. 11.

## 4.3. Memory and I/O Resources

#### 4.3.1. General Memory Layout and Configuration

The IPC/REL12 board does not use any memory resources.

#### 4.3.2. General I/O Layout and Configuration

| Register Number | READ Registers          | WRITE Registers         |

|-----------------|-------------------------|-------------------------|

| 00H             | Status Register         | reserved                |

| 01H             | Control Register        | Control Register        |

| 02H             | Function ID Register    | reserved                |

| 03H             | Revision ID Register    | reserved                |

| 04H             | Relay Outputs 07        | Relay Outputs 07        |

| 05H             | Relay Outputs 811       | Relay Outputs 811       |

| 06H             | Transistor Outputs L0L7 | Transistor Outputs L0L7 |

| 07H             | reserved                | reserved                |

| 08-0FH          | reserved                | reserved                |

Tab. 8 I/O Address Space Layout

| Register | Bit   | Meaning                   | Programming                                 |

|----------|-------|---------------------------|---------------------------------------------|

| 00H      | D0    | reserved                  | = always 1                                  |

|          | D1    | reserved                  | = always 1                                  |

|          | D2    | reserved                  | = always 1                                  |

|          | D3    | reserved                  | = always 1                                  |

|          | D4    | not used                  | = always 1                                  |

|          | D5    | not used                  | = always 1                                  |

|          | D6    | not used                  | = always 1                                  |

|          | D7    | not used                  | = always 1                                  |

|          |       |                           |                                             |

| 01H      | D0    | reserved                  | reserved                                    |

|          | D1    | reserved                  | reserved                                    |

|          | D2    | FREEZE                    | = 0: outputs reset on STOP* active          |

|          |       | STOP mode                 | = 1: outputs freeze on STOP* active         |

|          |       |                           | Default = 0 (outputs reset on STOP* active) |

|          | D3D7  | not used                  | = always 1                                  |

|          |       |                           |                                             |

| 02H      | D0-D7 | FID                       | = EEH                                       |

|          |       |                           |                                             |

| 03H      | D0-D7 | RID                       | revision ID (see table 16)                  |

|          |       |                           |                                             |

| 04H      | D0-D7 | Read back of Register 04H | D0 = REL0, D7 = REL7 (Tab. 10)              |

|          |       |                           |                                             |

| 05H      | D0-D7 | Read back of Register 05H | D0 = REL8, D3 = REL11 (Tab. 10)             |

|          |       |                           | (D4D7 = 0)                                  |

|          |       |                           |                                             |

| 06H      | D0-D7 | Read back of Register 06H | D0 = L0, D7 = L7                            |

|          |       |                           | 0 = output OFF, 1 = output ON               |

|          |       |                           |                                             |

| 07H      | D0-D7 | reserved                  |                                             |

|          |       |                           |                                             |

| 08H-0FH  | D0-D7 | reserved                  |                                             |

Tab. 9 Utilization of the individual Bit (READ-Registers)

| Register | Bit   | Meaning                    | Programming                                 |

|----------|-------|----------------------------|---------------------------------------------|

|          |       |                            |                                             |

| 00H      | D0D7  | not used                   |                                             |

|          |       |                            |                                             |

| 01H      | D0    | reserved                   | not used                                    |

|          | D1    | reserved                   | not used                                    |

|          | D2    | FREEZE                     | = 0: outputs reset on STOP* active          |

|          |       | STOP mode                  | = 1: outputs freeze on STOP* active         |

|          |       |                            | Default = 0 (outputs reset on STOP* active) |

|          | D3D7  | reserved                   |                                             |

|          |       |                            |                                             |

| 02H      | D0-D7 | reserved                   | not used                                    |

|          |       |                            |                                             |

| 03H      | D0-D7 | not used                   |                                             |

|          |       |                            |                                             |

| 04H      | D0-D7 | Relays Outputs             | D0 = REL0, D7 = REL7 (Tab. 10)              |

|          |       | (REL0 REL7)                |                                             |

|          |       |                            |                                             |

| 05H      | D0-D7 | Relays Outputs             | D0 = REL8, D3 = REL11 (Tab. 10)             |

|          |       | (REL8 REL11)               | (D4D7 = 0)                                  |

|          |       |                            |                                             |

| 06H      | D0-D7 | Transistor Outputs (L0 L7) | D0 = L0, D7 = L7                            |

|          |       |                            | 0 = output OFF, 1 = output ON               |

|          |       |                            |                                             |

| 07H      | D0-D7 | reserved                   | do not write                                |

|          |       |                            |                                             |

| 08H-0FH  | D0-D7 | reserved                   | do not write                                |

Tab. 10 Utilization of the individual Bit (WRITE-Registers)

| Bit in Register         | relay make contact | relay break contact |

|-------------------------|--------------------|---------------------|

| Output "0" (= inactive) | open               | closed              |

| Output "1" (= active)   | closed             | open                |

Tab. 11 Interface Specifications and Programming for Relay Outputs

# 5 Technical Data

#### 5.1. General Electrical Data

#### **Important Note**

Do not operate the REL12 board outside of the recommended operating conditions. Otherwise lifetime and performance will degrade.

Operating the board outside of the absolute maximum ratings may damage the hardware.

## Absolute Maximum Ratings (over free-air temperature range)

| Parameter                                          | Symbol | min  | nom | max | Unit |

|----------------------------------------------------|--------|------|-----|-----|------|

| internal power supply voltage                      | Vcc    | -0.5 |     | 5.5 | Vdc  |

| relay switching voltage                            | Vr     |      |     | 48  | Vdc  |

| relay switching current (at 48Vdc)                 | Ir     |      |     | 1   | A    |

| relay switching current (at 24Vdc)                 | Ir     |      |     | 2   | A    |

| transistor output collector-emitter voltage        | Vce    |      |     | 48  | Vdc  |

| transistor output sink current                     | Itr    |      |     | 100 | mA   |

| clamping current on Vext pin                       | Icl    |      |     | 500 | mA   |

| isolation logic to chassis                         |        | 1000 |     |     | Vrms |

| (AC, 60s, 500m a.s.l., Ta=25°C)                    |        |      |     |     |      |

| isolation relay contacts to logic                  |        |      |     |     | Vrms |

| (AC, 60s, 500m a.s.l., Ta=25°C)                    |        | 1500 |     |     |      |

| isolation relay contacts to chassis                |        |      |     |     | Vrms |

| (AC, 60s, 500m a.s.l., Ta=25°C)                    |        | 500  |     |     |      |

| creepage distance logic to chassis and PCB boarder |        | 1.5  |     |     | mm   |

| creepage distance relay contacts to logic          |        | 2.4  |     |     | mm   |

| creepage distance relay contacts to chassis        |        | 1.3  |     |     | mm   |

| creepage distance between two different relay      |        |      |     |     | mm   |

| contacts                                           |        | 0.5  |     |     |      |

| storage temperature range                          | Tst    | -40  |     | 90  | °C   |

Tab. 12 General Absolute Maximum Ratings

## **Recommended Operating Conditions**

| parameter                                   | symbol | min  | nom  | max  | unit |

|---------------------------------------------|--------|------|------|------|------|

| logic supply voltage                        | Vcc    | 4.75 | 5.00 | 5.25 | V    |

| relay switching voltage                     | Vr     |      |      | 48   | Vdc  |

| relay switching current (at 48Vdc)          | Ir     |      |      | 1    | A    |

| relay switching current (at 24Vdc)          | Ir     |      |      | 2    | A    |

| transistor output collector-emitter voltage | Vce    |      |      | 48   | Vdc  |

| transistor output sink current              | Itr    |      |      | 100  | mA   |

| operating free air temperature              | Ta     | -40  |      | 85   | °C   |

| extended range product                      |        |      |      |      |      |

Tab. 13 General Recommended Operating Conditions

# Electrical Characteristics (over recommended operating range, unless otherwise noted)

| Parameter                                        | Symbol   | min | typ  | max | Unit |

|--------------------------------------------------|----------|-----|------|-----|------|

| logic supply current (Vcc=5V, all outputs off)   | Icc      |     | 65   | 100 | mA   |

| logic supply current (Vcc=5V, all outputs on, no | Icc      |     | 400  |     | mA   |

| loads on P2 pullups)                             |          |     |      | 500 |      |

| initial relay contact resistance (10mA/20mV)     | Rmax     |     | < 50 |     | mOhm |

| minimum switching voltage                        |          |     | 100  |     | uVdc |

| transistor output saturation voltage             | Vce(sat) |     | 1    |     | V    |

| pullup resistors to Vcc on P2 (each of 8 pins)   | Rpu      |     | 270  |     | Ohm  |

Tab. 14 General Electrical Characteristics

# **Switching Characteristics (nominal conditions)**

| Parameter                                 | Symbol  | min | typ | max |    |

|-------------------------------------------|---------|-----|-----|-----|----|

| relay switch on delay                     | ton     |     | 1   | 4   | ms |

| relay switch off delay                    | toff    |     | 3   | 6   | ms |

| relay bounce time                         | tbounce |     | 1   | 5   | ms |

| relay maximum switching rate without load | fmax    |     |     | 50  | Hz |

Tab. 15 General Switching Characteristics

# 5.2. Mechanical Data

Fig. 5 Mechanical Outline

# 6 Firmware

The IPC/REL12 board does not contain any firmware.

# 7 Product Revision History

#### 7.1. Hardware

This paragraph lists the different hardware revisions of the IPC/REL12 boards delivered beginning with the first production lot. Note that prototyping boards are not included and must be returned to factory for upgrade or replacement. All information listed in this document relies on definitive state hardware. Therefore this information may be incompatible with the prototyping board hardware.

#### **Important Note**

This document always covers the newest product revision listed in Tab. 15. Please contact the manufacturers technical support for upgrade options.

| Board Identification (see product label) | Product<br>Revision | Revision<br>ID | Remarks          |

|------------------------------------------|---------------------|----------------|------------------|

|                                          |                     | Register       |                  |

| IPC/REL12-1AE #1                         | #1                  | 01H            | Original Release |

|                                          |                     |                |                  |

Tab. 16 Hardware Revision State

#### 7.2. Firmware

The IPC/REL12 board does not contain any firmware.

# 8 Manufacturer Information

#### 8.1. Contact

Our distributors and system integrators will gladly give you any information about our products and their use. If you want to contact the manufacturer directly, please send a fax or email message containing a short description of your application and your request to the following address or use one of the information or technical support request forms on our internet homepage:

Syslogic Datentechnik AG Täfernstr. 28 CH-5405 Baden-Dättwil / Switzerland

Email: <a href="mailto:support@syslogic.ch">support@syslogic.ch</a>

www: <a href="http://www.syslogic.ch">http://www.syslogic.ch</a>

Tel: +41 56 200 9040

Fax: +41 56 200 9050

#### 8.2. Warranty

Our products are covered by a world-wide manufacturers warranty. The warranty period starts at the delivery time from our official distributor to the customer. The duration of the warranty period is specified in the respective product catalogs and the offers. All products carry a date code and a job number for identification. The manufacturing data and deliveries are registered in a high level Quality Management System.

The warranty covers material and manufacturing defects. All products must be returned via the official distributor to the factory for repair or replacement. The warranty expires immediately if the products are damaged of operation outside of the specified recommended operating conditions. The warranty also expires if the date code or job number listed on the product is altered or rendered unintelligible. The warranty does not include damage due to errors in firmware or software delivered with the products.